CIS 310 Operating Systems Week 10: Virtual *Memory*

Dr. Brian C. Ladd

Friday 5<sup>th</sup> November, 2021

Dr. Brian C. Ladd

CIS 310 Operating Systems

Friday 5<sup>th</sup> November, 2021 1/1

< 回 > < 三 > < 三 >

### Outline

◆□ > ◆□ > ◆臣 > ◆臣 > ○ 臣 ○ の Q @

Creates a *new* process control block (PCB).

PCB — OS-specific data structure; access must be privileged.

fork() is a library wrapper around a *system call*.

イロト イポト イヨト イヨト

- Creates a *new* process control block (PCB).

PCB OS-specific data structure; access must be privileged.

fork() is a library wrapper around a *system call*.

- Trap to the OS. k-stack saved to current (parent) PCB.

- Creates a *new* process control block (PCB).

PCB OS-specific data structure; access must be privileged.

fork() is a library wrapper around a *system call*.

- Trap to the OS. k-stack saved to current (parent) PCB.

- Duplicate parent PCB, duplicate all FD, duplicate memory assignment but separate writable pages.

(日)

- Creates a new process control block (PCB).

PCB OS-specific data structure; access must be privileged.

fork() is a library wrapper around a system call.

- Trap to the OS. k-stack saved to current (parent) PCB.

- Duplicate parent PCB, duplicate all FD, duplicate memory assignment but separate writable pages.

- **Policy** Prefer parent or child process by returning from the system call to one or the other.

・ロト ・四ト ・ヨト

Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a *system call*.

(日)

- Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a *system call*.

- Trap to the OS. Save context to PCB. Release user memory (will keep FD and most of the PCB the same).

Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a system call.

- Trap to the OS. Save context to PCB. Release user memory (will keep FD and most of the PCB the same).

- Load beginning of the *code* segment of cmd file. Allocate new memory for *heap* and *stack* for a new program.

Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a *system call*.

- Trap to the OS. Save context to PCB. Release user memory (will keep FD and most of the PCB the same).

- Load beginning of the *code* segment of cmd file. Allocate new memory for *heap* and *stack* for a new program.

- Put the string cmd and provided arguments in memory according to OS convention.

Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a *system call*.

- Trap to the OS. Save context to PCB. Release user memory (will keep FD and most of the PCB the same).

- Load beginning of the *code* segment of cmd file. Allocate new memory for *heap* and *stack* for a new program.

- Put the string cmd and provided arguments in memory according to OS convention.

- Modify context so IP contains the virtual starting address for a new program.

イロト イヨト イヨト

Loads new program code into memory and starts the loaded program from the beginning.

Will read from *filesystem*. Will modify *context*. Privileged operations.

exec() is a library wrapper around a system call.

- Trap to the OS. Save context to PCB. Release user memory (will keep FD and most of the PCB the same).

- Load beginning of the *code* segment of cmd file. Allocate new memory for *heap* and *stack* for a new program.

- Put the string cmd and provided arguments in memory according to OS convention.

- Modify context so IP contains the virtual starting address for a new program.

- Return from interrupt.

イロト イボト イヨト イヨト

### Address Space

#### Definition

An address space is *all* of the memory that a (process/machine) can **address**.

- If the addresses refer to actual RAM locations, they are **physical** addresses in a physical address space.

- If the addresses must be translated before they refer to actual RAM locations, they are **virtual** addresses in a virtual address space.

The *size* of an address space is determined by the number of address bits it has: n **bits** of address  $\Rightarrow 2^n$  **bytes** of memory.

< ロ > < 同 > < 回 > < 回 >

• Virtualization should be *transparent*.

э

- Virtualization should be *transparent*.

- The *process* sees a single, contiguous address space beginning at 0 (hex).

- Virtualization should be *transparent*.

- The process sees a single, contiguous address space beginning at 0 (hex).

- All addresses in the process (contents of IP, pointers, load/store instruction targets) are *virtual*.

(日)

- Virtualization should be *transparent*.

- The process sees a single, contiguous address space beginning at 0 (hex).

- All addresses in the process (contents of IP, pointers, load/store instruction targets) are *virtual*.

- Indirect addressing, through an OS-supported translator, is always applied for user-space machine code.

(日)

Base Register

• A **base register** is a CPU or MMU register that permits dynamic memory relocation.

э

イロト イボト イヨト イヨト

Base Register

- A **base register** is a CPU or MMU register that permits dynamic memory relocation.

- The *physical* address is calculated by **adding** the *virtual* address to the value in the base register.

Base Register

- A **base register** is a CPU or MMU register that permits dynamic memory relocation.

- The *physical* address is calculated by **adding** the *virtual* address to the value in the base register.

- The base register alone can permit user programs to generate dangerous addresses.

Base Register

- A **base register** is a CPU or MMU register that permits dynamic memory relocation.

- The *physical* address is calculated by **adding** the *virtual* address to the value in the base register.

- The base register alone can permit user programs to generate dangerous addresses.

- Combined with a **bounds register**, the translation is much safer.

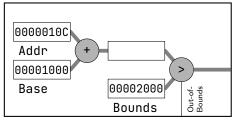

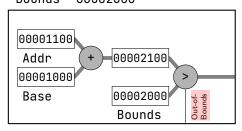

#### Fetch

IP 0000010C Base 00001000

Bounds 00002000

3

イロト イボト イヨト イヨト

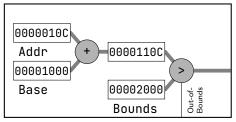

#### Fetch

IP 0000010C Base 00001000

Bounds 00002000

3

イロト 不得 トイヨト イヨト

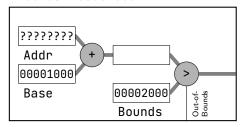

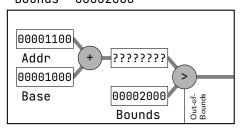

load R1, 0x00001100 Base 00001000 Bounds 00002000

3

イロト イポト イヨト イヨト

load R1, 0x00001100 Base 00001000 Bounds 00002000

3

イロト 不得 トイヨト イヨト

load R1, 0x00001100 Base 00001000 Bounds 00002000

イロト 不得 トイヨト イヨト 二日

• Using a single base/bounds register pair for a process permits dynamic relocation of the *whole virtual address space*.

- Using a single base/bounds register pair for a process permits dynamic relocation of the *whole virtual address space*.

- This requires contiguous **physical** memory that can contain the **virtual** address space.

- Using a single base/bounds register pair for a process permits dynamic relocation of the *whole virtual address space*.

- This requires contiguous **physical** memory that can contain the **virtual** address space.

- Fixed size process spaces will probably over allocate for many processes, wasting memory in *internal* fragmentation.

- Using a single base/bounds register pair for a process permits dynamic relocation of the *whole virtual address space*.

- This requires contiguous **physical** memory that can contain the **virtual** address space.

- Fixed size process spaces will probably over allocate for many processes, wasting memory in *internal* fragmentation.

- Variable-size process spaces will lead to *external* fragmentation.

• Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Can break down by **segment**.

(日)

- Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Can break down by **segment**.

- With four base registers, the left-most pair of bits would indicate which segment base to use for relocation.

(4) (日本)

- Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Can break down by segment.

- With four base registers, the left-most pair of bits would indicate which segment base to use for relocation.

- The OS can allocate four blocks, each a quarter of the size of the virtual address space, for the process.

- Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Can break down by segment.

- With four base registers, the left-most pair of bits would indicate which segment base to use for relocation.

- The OS can allocate four blocks, each a quarter of the size of the virtual address space, for the process.

- Still variable size. Can still fragment.

- 4 回 ト 4 ヨ ト 4 ヨ ト

- Easier to fit if virtual address space is broken down into multiple pieces, each with it's own base/bounds pair.

- Can break down by segment.

- With four base registers, the left-most pair of bits would indicate which segment base to use for relocation.

- The OS can allocate four blocks, each a quarter of the size of the virtual address space, for the process.

- Still variable size. Can still fragment.

- **Speed**: Another problem is speed of addition.  $O(\log(bits))$

• Avoid external fragmentation by only allocating a single size of block.

- Avoid external fragmentation by only allocating a single size of block.

- Big block v. small block

- Avoid external fragmentation by only allocating a single size of block.

- Big block v. small block

- Big: fewer base registers needed; more internal fragmentation

- Avoid external fragmentation by only allocating a single size of block.

- Big block v. small block

- Big: fewer base registers needed; more internal fragmentation

- Small: less internal fragmentation; more base registers

- Avoid external fragmentation by only allocating a single size of block.

- Big block v. small block

- Big: fewer base registers needed; more internal fragmentation

- Small: less internal fragmentation; more base registers

- Small *page size* with translation information accessed indirectly from RAM is **paged virtual memory**.

• A page table base register (PTBR) is a CPU or MMU register that contains the **physical** address of the beginning of the *page table*.

- A page table base register (PTBR) is a CPU or MMU register that contains the **physical** address of the beginning of the *page table*.

- The PTBR is part of the context for a process; the page table is a *per process* data structure.

- A page table base register (PTBR) is a CPU or MMU register that contains the **physical** address of the beginning of the *page table*.

- The PTBR is part of the context for a process; the page table is a *per process* data structure.

- Address translation is done by separating addresses into two parts: the page/frame number and the offset.

<page #> <offset>

Only the page # is translated from the virtual to the physical address.

- A page table base register (PTBR) is a CPU or MMU register that contains the **physical** address of the beginning of the *page table*.

- The PTBR is part of the context for a process; the page table is a *per process* data structure.

- Address translation is done by separating addresses into two parts: the page/frame number and the offset.

<page #> <offset>

Only the page # is translated from the virtual to the physical address.

• The *offset* is a fixed number of bits wide so that the bounds register is no longer required.

(日)

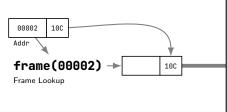

#### • Split virtual address: <page, offset>

(日)

- Split virtual address: <page, offset>

- Use page as an index into the page table array

- 20

イロト イボト イヨト イヨト

- Split virtual address: <page, offset>

- Use page as an index into the page table array

- Get frame out of page table entry

3

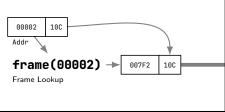

- Split virtual address: <page, offset>

- Use page as an index into the page table array

- Get frame out of page table entry

- Combine <frame, offset> into physical address

э

イロト イポト イヨト イヨト

Fetch

4KB

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

Page #:

- 31

イロト イボト イヨト イヨト

Fetch

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

Page #: 00002

Page: #: 00002

Offset:

イロト 不得下 イヨト イヨト 二日

Fetch

4KB

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

4B

Page #: 00002

4B

Offset: 10C

4D

Address of PTE:

4D

- 3

Fetch

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

Page #: 00002

Page #: 00002

Offset: 10C

Address of PTE: F0000000 +

F0000000 +

- 20

Fetch

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

Page #: 00002

Page #: 00002

Offset: 10C

Address of PTE: F0000000 + 4 ×

- 20

Fetch

Page Size

4KB

IP

0000210C

PTBR

F0000000

sizeof(PTE)

4B

Offset Bits: 12b

12b

Page #: 00002

00002

Offset: 10C

4ddress of PTE: F0000000 + 4 × 00002 =

- 31

# Fetch Page Size 4KB IP 0000210C PTBR F0000000 sizeof(PTE) 4B Offset Bits: 12b 120 Page #: 00002 0002 Offset: 10C 4ddress of PTE: F0000000 + 4 × 00002 = F0000008 RAM[F0000008] = 007F2

・ロト ・ 母 ト ・ ヨ ト ・ ヨ ト

#### Fetch Page Size 4KB TΡ 00002100 PTBR F0000000 sizeof(PTE) 4B Offset Bits: 12b Page #: 00002 Offset: 10C Address of PTE: $F0000000 + 4 \times 00002 = F0000008$ RAM[F0000008] = 007F2Physical Address:

・ロト ・ 母 ト ・ ヨ ト ・ ヨ ト

#### Fetch Page Size 4KB TΡ 00002100 PTBR F0000000 sizeof(PTE) 4B Offset Bits: 12b Page #: 00002 Offset: 10C Address of PTE: $F0000000 + 4 \times 00002 = F0000008$ RAM[F0000008] = 007F2Physical Address: 007F210C

・ロト ・ 母 ト ・ ヨ ト ・ ヨ ト

#### Fetch

| Page Size | 4KB      |  |

|-----------|----------|--|

| IP        | 0000210C |  |

| PTBR      | F0000000 |  |

|           |          |  |

# sizeof(PTE) 4B

э

・ロト ・ 四ト ・ ヨト ・ ヨト …

#### Fetch

| Page Size | 4KB      |  |

|-----------|----------|--|

| IP        | 0000210C |  |

| PTBR      | F0000000 |  |

|           |          |  |

# sizeof(PTE) 4B

| 1)r | Brian | add |

|-----|-------|-----|

|     |       |     |

э

・ロト ・ 四ト ・ ヨト ・ ヨト …